Meta ha annunciato Meta Training and Inference Accelerator, il suo chip di esecuzione di software per l’intelligenza artificiale. Questa ed altre notizie sono state date durante l’evento AI Intra@Scale del 18 maggio, occasione di annuncio non solo di MTIA ma anche di altre novità come lo Scalable Video Processor MSVP e anche architetture di data center di prossima generazione. Queste innovazioni saranno alla base dello sviluppo del metaverso e dei mondi virtuali che richiedono modelli di intelligenza artificiale più grandi di quelli attuali per modalità e parametri.

Tornando su MTIA, come dice Tiernan Ray su ZD Net, la peculiarità del chip è di essere adatto sia al training, sia all’esecuzione (inference). Un articolo completo sviluppato da Meta è disponibile qui. Molte altre informazioni saranno rivelate a Isca 23 il prossimo giugno.

Riassumiamo, in breve, la struttura del chip, soffermandoci poi sul core Risc-V e sul linguaggio Knyfe (sul quale non abbiamo grandi dettagli).

MTIA v1

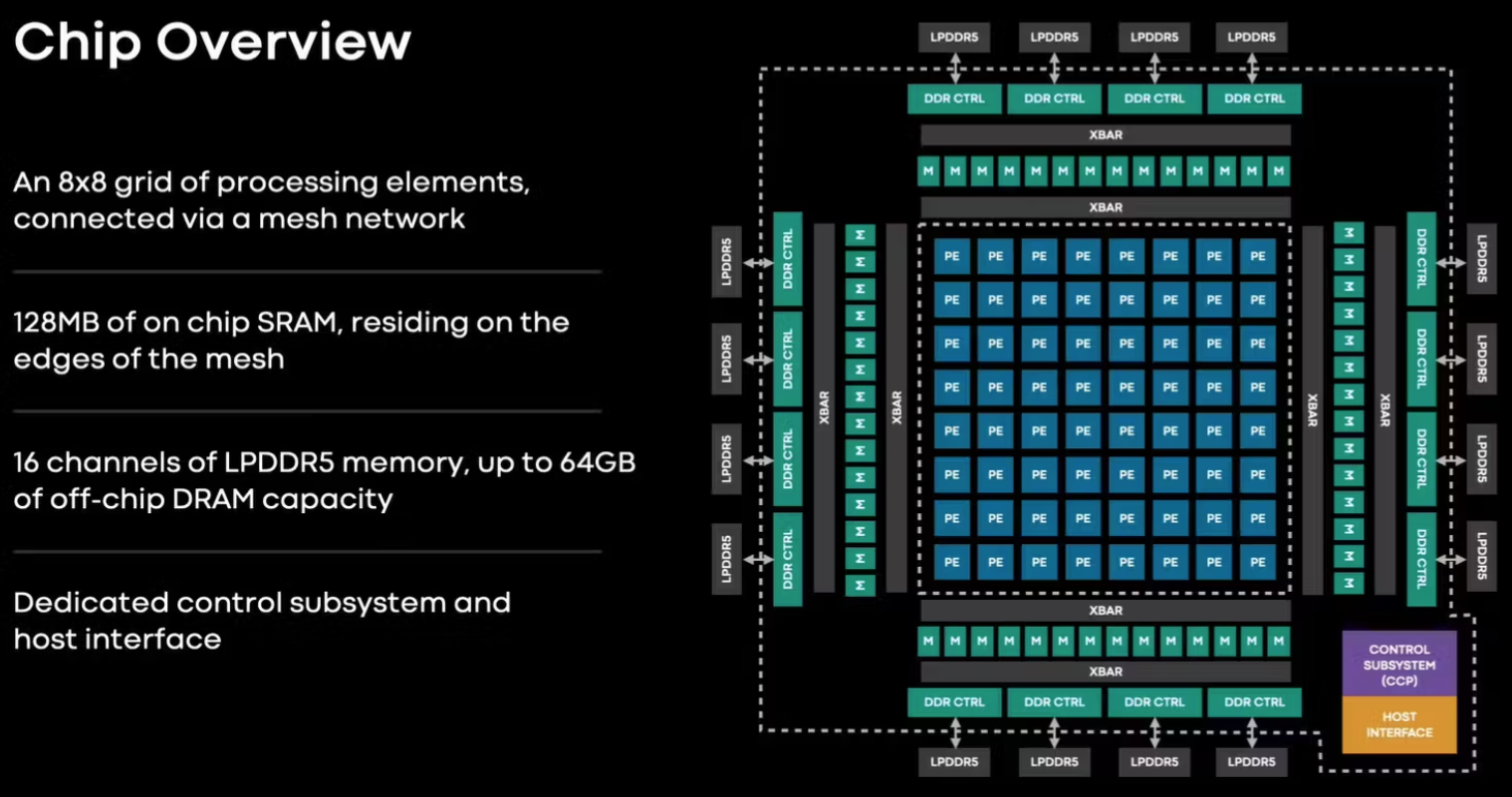

Il chip si basa su una griglia di 64 unità di elaborazione con intorno le varie unità complementari (controller, memoria etc). La griglia contiene 64 Processing Element (PE) organizzati in una configurazione 8×8. I PE sono collegati tra loro e ai blocchi di memoria tramite una rete mesh. La griglia può essere usata per un singolo lavoro su 64 core o essere suddivisa in più sottogriglie che possono eseguire lavori indipendenti.

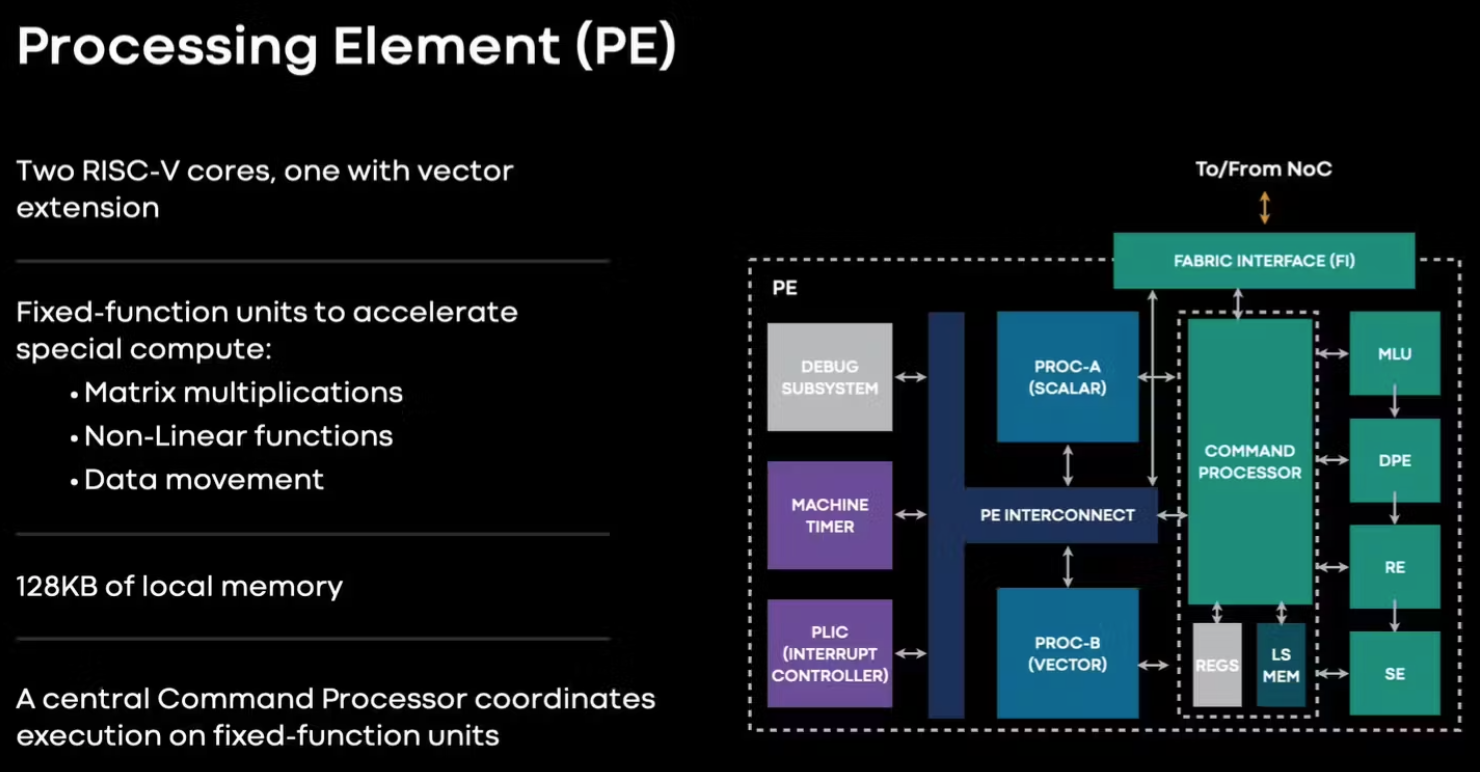

Ogni PE è dotato di due core del processore (uno dei quali dotato dell’estensione vettoriale) e di svariate unità ottimizzate su singole operazioni critiche (moltiplicazione di matrici, calcolo di funzioni non lineari ed altri). I core del processore si basano sull’architettura RISC-V.

Il chip fornisce parallelismo a livello sia di thread sia di dati, sulle istruzioni e sulla memoria.

Lo stack software di MTIA

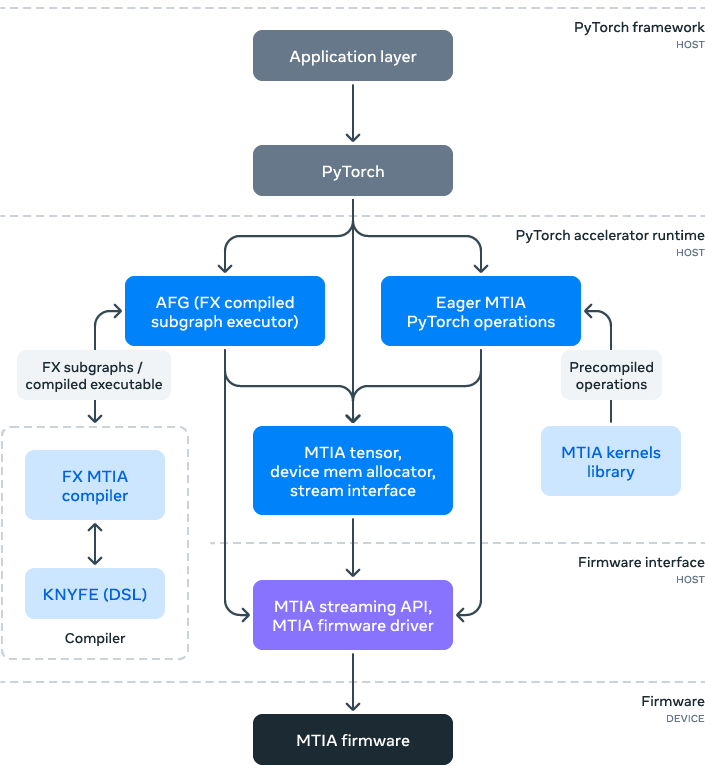

La base dello stack software è PyTorch, che si integra esattamente come per CPU o GPU. Lo stack fornisce anche la sincronizzazione e la comunicazione necessarie tra più schede acceleratrici.

Esistono diversi modi per creare kernel di calcolo che possono essere eseguiti sull’acceleratore, ovvero PyTorch, C/C++ (per kernel ottimizzati a mano) e un nuovo linguaggio specifico del dominio chiamato KNYFE.

L’unica informazione che abbiamo su KNYFE è che “richiede una descrizione ad alto livello di un operatore ML come input e genera codice kernel C++ ottimizzato di basso livello. Questo codice di basso livello sfrutta la toolchain del compilatore LLVM open source con estensioni MTIA per produrre eseguibili efficienti per i core del processore all’interno dei PE”.

Meta ha anche sviluppato una libreria di kernel ottimizzati a mano e altamente ottimizzati per kernel ML critici per le prestazioni, come operatori completamente connessi e incorporati.

Risc V

Una particolarità dei PE è che non usano l’onnipresente Arm, ma l’astro “nascente” Risc V. Al di là della sua storia, il Risc V è interessante perché ha una sua filiera che non passa forzatamente per Taiwan.

Risc V nasce nel 2010 nel Parc Lab dell’Università di Berkeley. All’interno di un budget quinquennale per l’elaborazione parallela, il dipartimento diretto dall’inventore del termine Risc si trova alla fine con un core risc open source, il linguaggio di descrizione dell’hardware Chisel e ovviamente lo Unix BSD (di Berkeley).

Il set d’istruzioni e l’architettura non sono innovativi, ma sono del tutto open source. Il progetto cresce e via via acquisisce strumenti software di diffusione maggiore del BSD Unix.

Come nota di cronaca, secondo alcuni esperti, somiglia molto al Risc-V la parte scalare delle istruzioni del Tesla D1.

Risc-V è su un percorso di forte crescita. Il Wilson Research Group/Siemens ha scoperto che il 23% dei progetti ASIC e FPGA ha incorporato RISC-V in almeno un processore in uno studio del 2020.

Semico Research prevede che il mercato consumerà 62,4 miliardi di core CPU RISC-V entro il 2025, un CAGR 2018-2025 del 146,2%. In testa c’è il settore industriale, con 16,7 miliardi di core. Negli ultimi tempi la crescita di Risc-V viene vista in avvicinamento a quella di Arm.